STM32 DAC.

Ключевое отличие цифровой электроники от аналоговой заключается в том, что цифровая электроника оперирует лишь двумя уровнями сигнала логическим нулем и единицей. Это не значит, что если мы подключим к ножке микроконтроллера мультиметр, он покажет 0 или 1V. Нуль, образно говоря, можно представить как отсутствие сигнала, а единица как присутствие сигнала, величина же самого сигнала зависит от питающего напряжения микросхемы. Если Ваш МК питается от 3V, то логический нуль будет соответствовать 0V, а логическая единица 3V. Для получения промежуточных значений напряжения на выводе микроконтроллера используют DAC или по-русски ЦАП.

DAC у STM32 обладает следующими особенностями:

Сразу хотелось бы отметить, что данные сначала загружаются в регистр предварительного хранения (data holding register, DHRx), и лишь потом по событию (если включено) переносятся в выходной регистр (DORx).

Регистр управления DAC_CR:

DMAEN2 (DAC channel2 DMA enable) — единица в этом бите разрешает использовать DMA.

MAMP2[3:0](DAC channel2 mask/amplitude selector) — битовое поле позволяет задавать амплитуду генерируемого.

WAVE2[1:0](DAC channel2 noise/triangle wave generation enable) — битовое поле позволяет включать аппаратный генератор и выбирать форму генерируемого сигнала. 0 — аппаратный генератор отключен, 1 — генерация шума, 2 — генерация пилы.

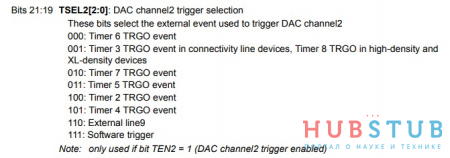

TSEL2[2:0](DAC channel2 trigger selection) — битовое поле позволяет выбрать источник события по которому данные будут переносится из регистра предварительно хранения (data holding register, DHRx), в выходной регистр (DORx).

TEN2(DAC channel2 trigger enable) — единица в этом бите включает перенос данных из регистра предварительно хранения (data holding register, DHRx), в выходной регистр (DORx) по триггеру. Если событие аппаратное это занимает 3 такта, если программное то 1.

BOFF2(DAC channel2 output buffer disable) — единица в этом бите, отключает буфер на выходе ЦАП, по умолчанию он включен.

EN2(DAC channel2 enable) — единица в этом бите запускает ЦАП.

Образно, регистр можно разделить на две части, они полностью идентичны, но настраивают разные каналы.

DMAEN1(DAC channel1 DMA enable) —

MAMP1[3:0](DAC channel1 mask/amplitude selector) —

WAVE1[1:0](DAC channel1 noise/triangle wave generation enable) —

TSEL1[2:0](DAC channel1 trigger selection) —

TEN1(DAC channel1 trigger enable) —

BOFF1(DAC channel1 output buffer disable) —

EN1(DAC channel1 enable) —

Регистр управления программным триггером DAC_SWTRIGR:

SWTRIG2(DAC channel2 software trigger) — при записи единицы в этот бит генерируется программное событие для второго канала.

SWTRIG1(DAC channel1 software trigger) — при записи единицы в этот бит генерируется программное событие для первого канала.

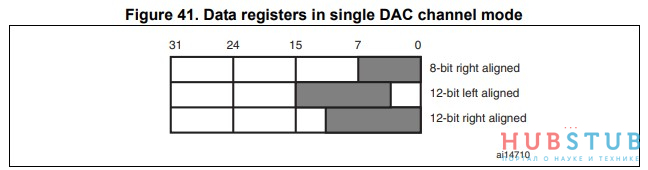

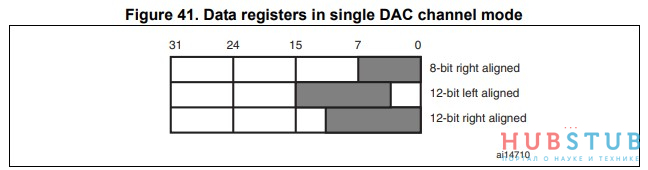

Данные в регистр предварительного хранения могут загружаться в нескольких форматах: 12 бит выравнивание по правому краю, 12 бит выравнивание по левому краю , 8 бит. Для каждого способа существует свой регистр, что значительно упрощает настройку.

DAC_DHR12Rx — предназначен для загрузки 12 бит выровненных по правому краю.

DAC_DHR12Lx — предназначен для загрузки 12 бит выровненных по левому краю.

DAC_DHR8Rx — предназначен для загрузки 8 бит выровненных по правому краю.

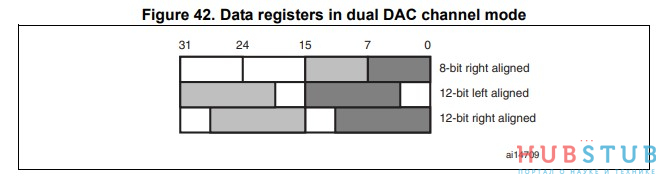

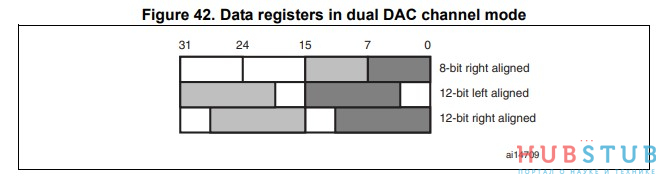

Если данные обоих ЦАП необходимо обновить одновременно, это можно сделать используя следующие регистры.

DAC_DHR12RD — предназначен для одновременного обновления обоих каналов, 12 бит выровненных по правому краю.

DAC_DHR12LD — предназначен для одновременного обновления обоих каналов, 12 бит выровненных по левому краю.

DAC_DHR8RD — предназначен для одновременного обновления обоих каналов, 8 бит выровненных по правому краю.

Регистр данных DAC_DOR1 — позволяет считывать текущее состояние выхода первого ЦАП.

Регистр данных DAC_DOR2 — позволяет считывать текущее состояние выхода второго ЦАП.

Мне ЦАП понадобился для получения напряжения величиной 1V на ножке МК. Код ниже позволяет это сделать.

DAC у STM32 обладает следующими особенностями:

- двухканальный 12 разрядный, может работать в 8 или 12-битном режиме

- напряжение на выходе от 0 до Vref

- аппаратная генерация шума и пилы

- одновременная загрузка данных в оба DAC

- отдельный DMA канал на каждый DAC

- запуск преобразования по триггеру

Сразу хотелось бы отметить, что данные сначала загружаются в регистр предварительного хранения (data holding register, DHRx), и лишь потом по событию (если включено) переносятся в выходной регистр (DORx).

Регистр управления DAC_CR:

DMAEN2 (DAC channel2 DMA enable) — единица в этом бите разрешает использовать DMA.

MAMP2[3:0](DAC channel2 mask/amplitude selector) — битовое поле позволяет задавать амплитуду генерируемого.

WAVE2[1:0](DAC channel2 noise/triangle wave generation enable) — битовое поле позволяет включать аппаратный генератор и выбирать форму генерируемого сигнала. 0 — аппаратный генератор отключен, 1 — генерация шума, 2 — генерация пилы.

TSEL2[2:0](DAC channel2 trigger selection) — битовое поле позволяет выбрать источник события по которому данные будут переносится из регистра предварительно хранения (data holding register, DHRx), в выходной регистр (DORx).

TEN2(DAC channel2 trigger enable) — единица в этом бите включает перенос данных из регистра предварительно хранения (data holding register, DHRx), в выходной регистр (DORx) по триггеру. Если событие аппаратное это занимает 3 такта, если программное то 1.

BOFF2(DAC channel2 output buffer disable) — единица в этом бите, отключает буфер на выходе ЦАП, по умолчанию он включен.

EN2(DAC channel2 enable) — единица в этом бите запускает ЦАП.

Образно, регистр можно разделить на две части, они полностью идентичны, но настраивают разные каналы.

DMAEN1(DAC channel1 DMA enable) —

MAMP1[3:0](DAC channel1 mask/amplitude selector) —

WAVE1[1:0](DAC channel1 noise/triangle wave generation enable) —

TSEL1[2:0](DAC channel1 trigger selection) —

TEN1(DAC channel1 trigger enable) —

BOFF1(DAC channel1 output buffer disable) —

EN1(DAC channel1 enable) —

Регистр управления программным триггером DAC_SWTRIGR:

SWTRIG2(DAC channel2 software trigger) — при записи единицы в этот бит генерируется программное событие для второго канала.

SWTRIG1(DAC channel1 software trigger) — при записи единицы в этот бит генерируется программное событие для первого канала.

Данные в регистр предварительного хранения могут загружаться в нескольких форматах: 12 бит выравнивание по правому краю, 12 бит выравнивание по левому краю , 8 бит. Для каждого способа существует свой регистр, что значительно упрощает настройку.

DAC_DHR12Rx — предназначен для загрузки 12 бит выровненных по правому краю.

DAC_DHR12Lx — предназначен для загрузки 12 бит выровненных по левому краю.

DAC_DHR8Rx — предназначен для загрузки 8 бит выровненных по правому краю.

Если данные обоих ЦАП необходимо обновить одновременно, это можно сделать используя следующие регистры.

DAC_DHR12RD — предназначен для одновременного обновления обоих каналов, 12 бит выровненных по правому краю.

DAC_DHR12LD — предназначен для одновременного обновления обоих каналов, 12 бит выровненных по левому краю.

DAC_DHR8RD — предназначен для одновременного обновления обоих каналов, 8 бит выровненных по правому краю.

Регистр данных DAC_DOR1 — позволяет считывать текущее состояние выхода первого ЦАП.

Регистр данных DAC_DOR2 — позволяет считывать текущее состояние выхода второго ЦАП.

Мне ЦАП понадобился для получения напряжения величиной 1V на ножке МК. Код ниже позволяет это сделать.

#include "stm32f4xx.h"

void DAC_Init(void)

{

//разрешаем тактирование порта

RCC->AHB1ENR |= RCC_AHB1ENR_GPIOAEN;

//PA5 push-pull

GPIOA->MODER |= GPIO_MODER_MODER5_1;

GPIOA->OSPEEDR |= GPIO_OSPEEDER_OSPEEDR5;

GPIOA->PUPDR &= ~GPIO_PUPDR_PUPDR5;

//разрешаем тактироваине DAC

RCC->APB1ENR |= RCC_APB1ENR_DACEN;

//включаем DAC2

DAC->CR |= DAC_CR_EN2;

//загружаем 12 битные данные в регистр с правым выравниванием

DAC->DHR12R2 = 1000;

}

Похожие статьи