STM32 тактирование.

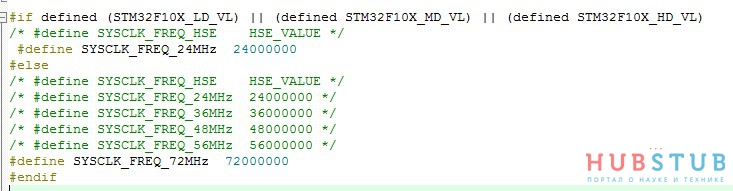

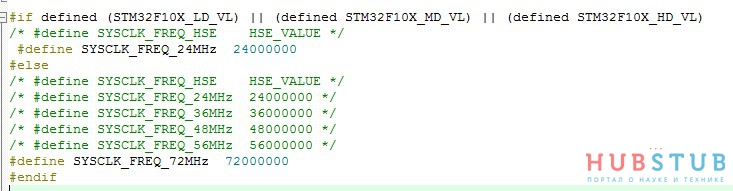

Первое время для того, чтобы упростить написание программ для STM32 не вдавался в тонкости настройки системы тактирования, а выбирал частоту системной шины в файле system_stm32f10x.c, просто раскоментировав нужную строку.

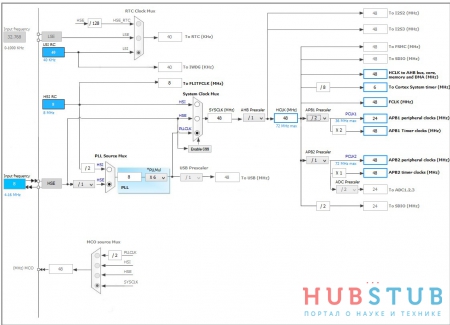

Но если уж доходило дело до настройки частоты тактирования отдельных блоков(например АЦП), то использовал CUBE.

Перед глазами вся система тактирования, что очень удобно и позволяет быстро разобраться какой коэффициент за, что отвечает.

Способ задания частоты системной шины, описанный выше, позволяет отлаживать программу только в железе потому, что при отладке в симуляторе флаг готовности того же HSE или PLL не кому установить.

Почему это я пишу про какие-то флаги?

Потому что на самом деле нет ни какой абракадабры и раскоментировав дефайн с нужной частотой тактирования, мы говорим препроцессору, что он должен включить в программу определенный участок кода. Если раскомментировать строку

#define SYSCLK_FREQ_56MHz 56000000

То препроцессор включит в программу следующий участок кода

Второе ограничение, к которому приводит такая настройка системной частоты — невозможно разогнать контроллер, потому как разгон производится с помощью настройки PLL, но в этом пока, что нужды не было.

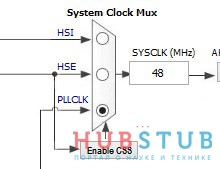

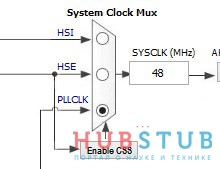

Итак, для формирования системной частоты(SYSCLK) могут использоваться три различных источника.(мы рассматриваем формирование SYSCLK так, как от неё через делители тактируется вся периферия)

HSI представляет собой внутренний RC генератор с частотой 8MHz. Он может выступать в качестве источник системной частоты, либо после деления на два подан на вход PLL. Надо отметить, что частота RC генератора зависит от температуры и может отклоняться от заданной от –1,9 до +1,3% при изменении температуры микроконтроллера от 0 до 70°C. При подаче, питающих напряжений, МК автоматически запускается от него.

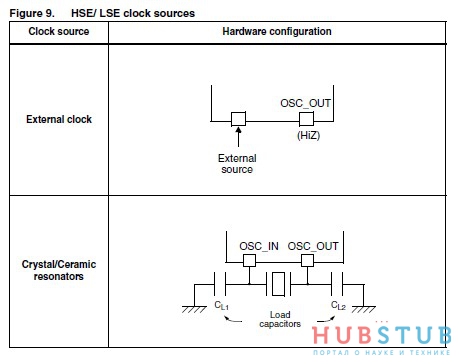

Что касается HSE тут возможны два варианта:

PLL – это банальный умножитель, с регулируемым коэффициентом умножения. То есть на его вход можно подать 8MHz, а на выходе получить частоту кратную 8, например 56MHz. Этого понимания достаточно для настройки PLL, хотя надо сказать, что само устройство PLL достаточно интересно и статью по его работе планирую опубликовать тут.

Еще, изменять коэффициенты PLL можно только при выключенном PLL, при запущенном PLL изменять коэффициенты нельзя.

Также хотелось бы отметить, что у МК есть ножка через которую можно тактировать различные устройства или просто посмотреть на какой частоте запустился МК, называется она МСО.

Еще интересной фичей является система защиты от нестабильной работы и отказа генератора HSE, называется она CSS(Clock security system).

CSS способна отслеживать отказ или нестабильную работу генератора HSE, осуществлять автоматическое переключение тактирования на встроенный генератор HSI и вызывать немаскируемые прерывания — NMI (Non-Masked Interrupts). Напомню, что NMI – это прерывания, которые невозможно сбросить, не обработав, то есть их возникновение прерывают выполнение программы независимо от каких-либо условий.

Регистр управления RCC_CR :

PLLRDY(PLL clock ready flag) — флаг готовности PLL, устанавливается аппаратно.

PLLON( PLL enable) — установка единицы в этот бит разрешает работу PLL.

CSSON(Clock security system enable) — установка единицы в этот бит разрешает работу детектора тактового сигнала от HSE.

HSEBYP(External high-speed clock bypass) — установка единицы в этот бит разрешает использование внешнего генератора и возможна лишь когда HSEON сброшен.

HSERDY(External high-speed clock ready flag) — единица в этом бите говорит о том, что внешний генератор стабилизировался.

HSEON(HSE clock enable) — установка единицы в этом бит, позволяет принудительно переключиться на внешний генератор.

HSICAL[7:0](Internal high-speed clock calibration) — эти биты инициализируются при запуске.

HSITRIM[4:0](Internal high-speed clock trimming) — значение этих битов прибавляется к значению HSICAL, таким появляется возможность корректировать частоту МК, которая может «уходить» в зависимости от напряжения питания и температуры окружающей среды. Шаг подстройки между двумя значениями примерно равен 40KHz.

HSIRDY(Internal high-speed clock ready flag) – флаг устанавливается аппаратно когда внутренний RC генератор 8 МГц стабилизировался.

HSION(Internal high-speed clock enable) — установка этого бита в единицу принудительно запускает внутренний RC генератор 8 МГц. Этот бит не может быть сброшен если с помощью HSI, формируется системная частота.

Регистр конфигурации RCC_CFGR:

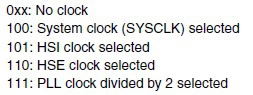

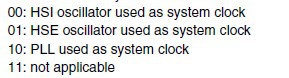

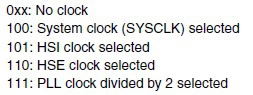

MCO(Microcontroller clock output) — значение этих битов определяют работу вывода MCO.

USBPRE(USB prescaler) — ноль в этом бите включает предделить с коэффициентом 1.5 для usb.Предделитель должен быть настроен до включения тактирования USB шины.

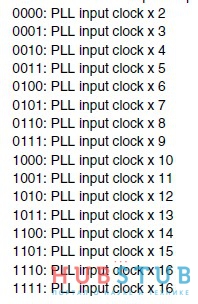

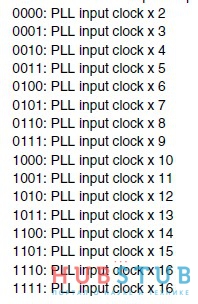

PLLMUL(PLL multiplication factor) — значение этих битов определяет коэффициент умножения PLL.

PLLXTPRE(HSE divider for PLL entry) — значение этого бита определяет будет ли HSE поделен на два, перед подачей на вход PLL. Устанавливать его нужно при отключенной PLL.

PLLSRC(PLL entry clock source) — значение этого бита определяет с какого источника будет подан сигнал на вход PLL.(0 – источник HSI/2, 1 – источник HSE)

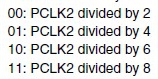

ADCPRE(ADC prescaler) — значение этих битов определяет коэффициент деления тактовой частоты для АЦП.

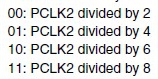

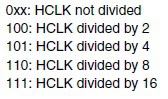

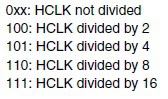

PPRE2(APB high-speed prescaler (APB2)) — значение этих битов определяет коэффициент деления тактовой частоты для APB2.

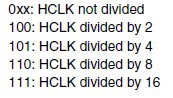

PPRE1(APB low-speed prescaler (APB1)) — значение этих битов определяет коэффициент деления тактовой частоты для APB1.

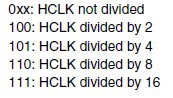

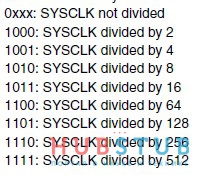

HPRE(AHB prescaler) — значение этих битов определяет коэффициент деления тактовой частоты для AHB.

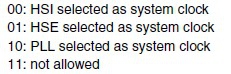

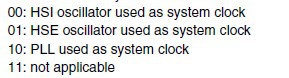

SWS(System clock switch status) — устанавливается аппаратно, показывая какой источник используется для тактирования системы.

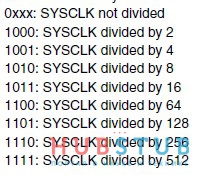

SW(System clock switch) — с помощью этих битов можно выбрать источник для тактирования SYSCLK.

Регистр прерываний RCC_CIR:

CSSC(Clock security system interrupt clear) — установка этого бита в единицу позволяет очистить флаг CSSF.

PLLRDYC(PLL ready interrupt clear) — установка этого бита в единицу позволяет очистить флаг PLLRDYF.

HSERDYC(HSE ready interrupt clear) — установка этого бита в единицу позволяет очистить флаг HSERDYF.

HSIRDYC(HSI ready interrupt clear) — установка этого бита в единицу позволяет очистить флаг HSIRDYF.

LSERDYC(LSE ready interrupt clear) — установка этого бита в единицу позволяет очистить флаг LSERDYF.

LSIRDYC(LSI ready interrupt clear) — установка этого бита в единицу позволяет очистить флаг LSIRDYF

PLLRDYIE(PLL ready interrupt enable) — единица в этом бите разрешает прерывания при сцеплении PLL.

HSERDYIE(HSE ready interrupt enable) — единица в этом бите разрешает прерывания при сцеплении HSE.

HSIRDYIE(HSI ready interrupt enable) — единица в этом бите разрешает прерывания при сцеплении HSI.

LSERDYIE(LSE ready interrupt enable) — единица в этом бите разрешает прерывания при сцеплении LSE.

LSIRDYIE(LSI ready interrupt enable) — единица в этом бите разрешает прерывания при сцеплении LSI.

CSSF(Clock security system interrupt flag) — этот флаг устанавливается аппаратно при отказе HSE, очищается с помощью CSSC.

PLLRDYF(PLL ready interrupt flag) — этот флаг устанавливается аппаратно если произошло сцеплении с PLL и бит PLLRDYDIE установлен..

HSERDYF(HSE ready interrupt flag) — этот флаг устанавливается аппаратно если HSE стабилизировался и бит HSERDYDIE установлен.

HSIRDYF(HSI ready interrupt flag) — этот флаг устанавливается аппаратно если HSI стабилизировался и бит HSIRDYDIE установлен..

LSERDYF(LSE ready interrupt flag) — этот флаг устанавливается аппаратно если LSE стабилизировался и бит LSERDYDIE установлен..

LSIRDYF(LSI ready interrupt flag) — этот флаг устанавливается аппаратно если LSI стабилизировался и бит LSIRDYDIE установлен.

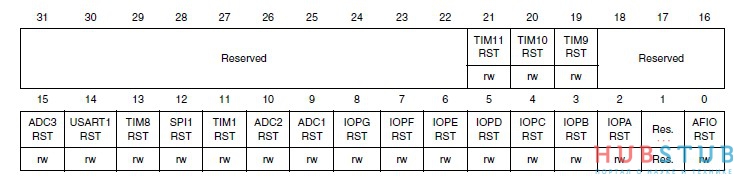

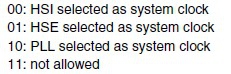

Регистр сброса RCC_APB2RSTR

При записи единицы в биты этого регистра происходит сброс соответствующей периферии, которая тактируется от шины APB2. Под сбросом понимается установка в регистры блока, например USART, значения по умолчанию.

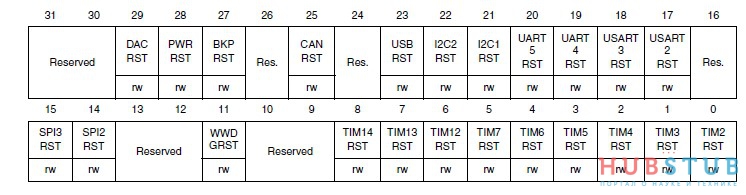

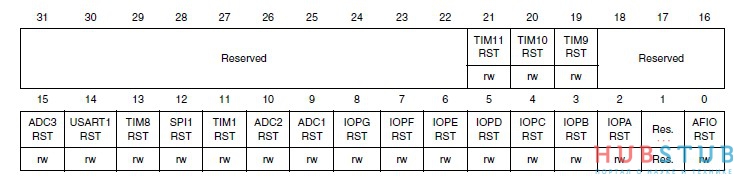

Регистр сброса RCC_APB1RSTR

При записи единицы в биты этого регистра происходит сброс соответствующей периферии, которая тактируется от шины APB1. Под сбросом понимается установка в регистры блока, например USART, значения по умолчанию.

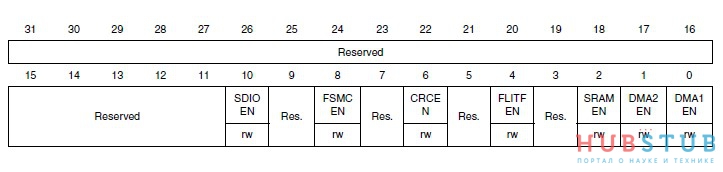

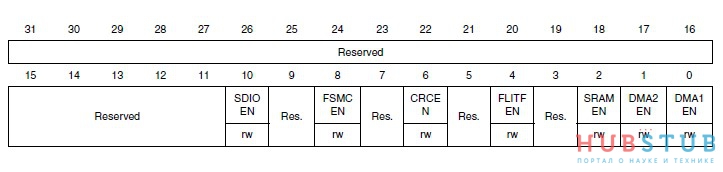

Регистр управления тактированием на шине AHB RCC_AHBENR

При записи единицы в биты этого регистра включается тактирование соответствующей периферии подключенной к шине AHB, при записи нуля отключается.

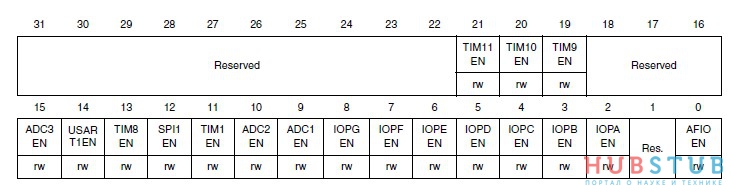

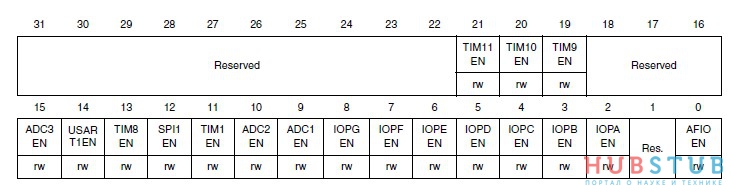

Регистр управления тактированием на шине APB2 RCC_APB2ENR

При записи единицы в биты этого регистра включается тактирование соответствующей периферии подключенной к шине APB2, при записи нуля отключается.

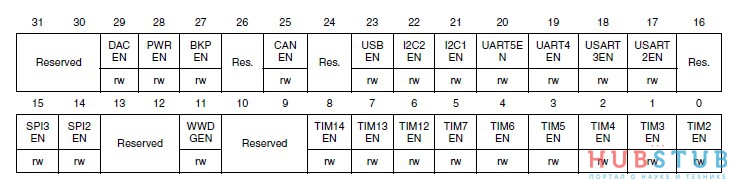

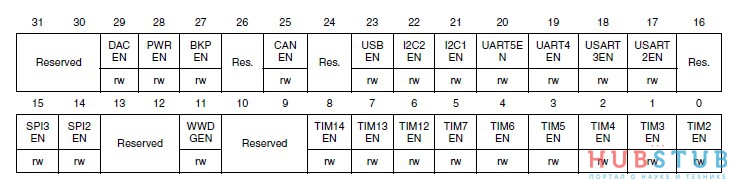

Регистр управления тактированием на шине APB1 RCC_APB1ENR

При записи единицы в биты этого регистра включается тактирование соответствующей периферии подключенной к шине APB1, при записи нуля отключается.

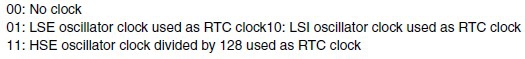

Регистр управления доменом BKP RCC_BDCR:

BDRST(Backup domain software reset) — установка единицы в этот бит сбрасывает значение битов регистра RCC_BDCR.

RTCEN(RTC clock enable) — установка единицы в этот бит включает тактирование RTC.

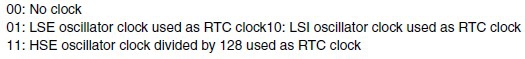

RTCSEL[1:0](RTC clock source selection) — значение этих битов определяет источник тактирования RTC.

LSEBYP(External low-speed oscillator bypass) — ставится и очищается программно, чтобы обойти LSE генератор в режиме отладки.

LSERDY(External low-speed oscillator ready) — единица в этом бите говорит о том, что LSE с частотой 32KHz стабилизировался.

LSEON(External low-speed oscillator enable) — установка единицы в этот бит разрешает работу LSE с частотой 32KHz.

Регистр управления/статуса RCC_CSR:

LPWRRSTF(Low-power reset flag) — этот флаг устанавливается аппаратно, когда происходит от контроллера пониженного потребления.

WWDGRSTF(Window watchdog reset flag) — этот флаг устанавливается аппаратно, когда происходит сброс от оконного WatchDog.

IWDGRSTF(Independent watchdog reset flag) — этот флаг устанавливается аппаратно, когда происходит сброс от независимого WatchDog.

SFTRSTF(Software reset flag) — этот флаг устанавливается аппаратно, когда происходит программный сброс.

PORRSTF(POR/PDR reset flag) — этот флаг устанавливается аппаратно при при включение/выключение питания.

PINRSTF(PIN reset flag) — этот флаг устанавливается аппаратно, когда происходит сброс от вывода NRST.

RMVF(Remove reset flag) — установка единицы в этот бит позволяет сбросить все, описанные выше флаги, в этот регистре.

LSIRDY(Internal low-speed oscillator ready) — единица в этом бите говорит о том, что LSI стабилизировался.

LSION(Internal low-speed oscillator enable) — установка единицы в этот бит разрешает работу внутреннего RC генератора 40 kHz.

На самом деле, до сих пор выбираю частоту тактирования системной шины в файле system_stm32f10x.c, просто раскоментировав нужную строку, но теперь это делаю осознано.

Но если уж доходило дело до настройки частоты тактирования отдельных блоков(например АЦП), то использовал CUBE.

Перед глазами вся система тактирования, что очень удобно и позволяет быстро разобраться какой коэффициент за, что отвечает.

Способ задания частоты системной шины, описанный выше, позволяет отлаживать программу только в железе потому, что при отладке в симуляторе флаг готовности того же HSE или PLL не кому установить.

Почему это я пишу про какие-то флаги?

Потому что на самом деле нет ни какой абракадабры и раскоментировав дефайн с нужной частотой тактирования, мы говорим препроцессору, что он должен включить в программу определенный участок кода. Если раскомментировать строку

#define SYSCLK_FREQ_56MHz 56000000

То препроцессор включит в программу следующий участок кода

Второе ограничение, к которому приводит такая настройка системной частоты — невозможно разогнать контроллер, потому как разгон производится с помощью настройки PLL, но в этом пока, что нужды не было.

Итак, для формирования системной частоты(SYSCLK) могут использоваться три различных источника.(мы рассматриваем формирование SYSCLK так, как от неё через делители тактируется вся периферия)

- HSI(high speed internal) oscillator clock

- HSE(high speed external) oscillator clock

- PLL clock

HSI представляет собой внутренний RC генератор с частотой 8MHz. Он может выступать в качестве источник системной частоты, либо после деления на два подан на вход PLL. Надо отметить, что частота RC генератора зависит от температуры и может отклоняться от заданной от –1,9 до +1,3% при изменении температуры микроконтроллера от 0 до 70°C. При подаче, питающих напряжений, МК автоматически запускается от него.

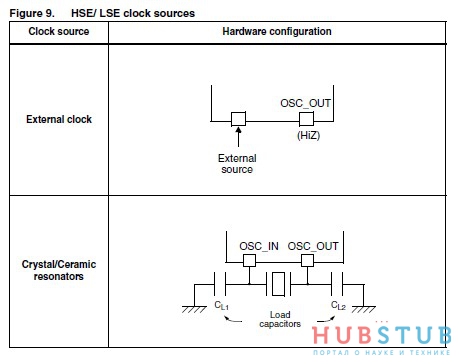

Что касается HSE тут возможны два варианта:

- подключение внешнего керамического/кварцевого резонатора с частотой от 4-16 MHz

- использование внешнего источника тактовых импульсов с коэффициентом заполнения примерно 50%

PLL – это банальный умножитель, с регулируемым коэффициентом умножения. То есть на его вход можно подать 8MHz, а на выходе получить частоту кратную 8, например 56MHz. Этого понимания достаточно для настройки PLL, хотя надо сказать, что само устройство PLL достаточно интересно и статью по его работе планирую опубликовать тут.

Еще, изменять коэффициенты PLL можно только при выключенном PLL, при запущенном PLL изменять коэффициенты нельзя.

Также хотелось бы отметить, что у МК есть ножка через которую можно тактировать различные устройства или просто посмотреть на какой частоте запустился МК, называется она МСО.

Еще интересной фичей является система защиты от нестабильной работы и отказа генератора HSE, называется она CSS(Clock security system).

CSS способна отслеживать отказ или нестабильную работу генератора HSE, осуществлять автоматическое переключение тактирования на встроенный генератор HSI и вызывать немаскируемые прерывания — NMI (Non-Masked Interrupts). Напомню, что NMI – это прерывания, которые невозможно сбросить, не обработав, то есть их возникновение прерывают выполнение программы независимо от каких-либо условий.

Регистр управления RCC_CR :

PLLRDY(PLL clock ready flag) — флаг готовности PLL, устанавливается аппаратно.

PLLON( PLL enable) — установка единицы в этот бит разрешает работу PLL.

CSSON(Clock security system enable) — установка единицы в этот бит разрешает работу детектора тактового сигнала от HSE.

HSEBYP(External high-speed clock bypass) — установка единицы в этот бит разрешает использование внешнего генератора и возможна лишь когда HSEON сброшен.

HSERDY(External high-speed clock ready flag) — единица в этом бите говорит о том, что внешний генератор стабилизировался.

HSEON(HSE clock enable) — установка единицы в этом бит, позволяет принудительно переключиться на внешний генератор.

HSICAL[7:0](Internal high-speed clock calibration) — эти биты инициализируются при запуске.

HSITRIM[4:0](Internal high-speed clock trimming) — значение этих битов прибавляется к значению HSICAL, таким появляется возможность корректировать частоту МК, которая может «уходить» в зависимости от напряжения питания и температуры окружающей среды. Шаг подстройки между двумя значениями примерно равен 40KHz.

HSIRDY(Internal high-speed clock ready flag) – флаг устанавливается аппаратно когда внутренний RC генератор 8 МГц стабилизировался.

HSION(Internal high-speed clock enable) — установка этого бита в единицу принудительно запускает внутренний RC генератор 8 МГц. Этот бит не может быть сброшен если с помощью HSI, формируется системная частота.

Регистр конфигурации RCC_CFGR:

MCO(Microcontroller clock output) — значение этих битов определяют работу вывода MCO.

USBPRE(USB prescaler) — ноль в этом бите включает предделить с коэффициентом 1.5 для usb.Предделитель должен быть настроен до включения тактирования USB шины.

PLLMUL(PLL multiplication factor) — значение этих битов определяет коэффициент умножения PLL.

PLLXTPRE(HSE divider for PLL entry) — значение этого бита определяет будет ли HSE поделен на два, перед подачей на вход PLL. Устанавливать его нужно при отключенной PLL.

PLLSRC(PLL entry clock source) — значение этого бита определяет с какого источника будет подан сигнал на вход PLL.(0 – источник HSI/2, 1 – источник HSE)

ADCPRE(ADC prescaler) — значение этих битов определяет коэффициент деления тактовой частоты для АЦП.

PPRE2(APB high-speed prescaler (APB2)) — значение этих битов определяет коэффициент деления тактовой частоты для APB2.

PPRE1(APB low-speed prescaler (APB1)) — значение этих битов определяет коэффициент деления тактовой частоты для APB1.

HPRE(AHB prescaler) — значение этих битов определяет коэффициент деления тактовой частоты для AHB.

SWS(System clock switch status) — устанавливается аппаратно, показывая какой источник используется для тактирования системы.

SW(System clock switch) — с помощью этих битов можно выбрать источник для тактирования SYSCLK.

Регистр прерываний RCC_CIR:

CSSC(Clock security system interrupt clear) — установка этого бита в единицу позволяет очистить флаг CSSF.

PLLRDYC(PLL ready interrupt clear) — установка этого бита в единицу позволяет очистить флаг PLLRDYF.

HSERDYC(HSE ready interrupt clear) — установка этого бита в единицу позволяет очистить флаг HSERDYF.

HSIRDYC(HSI ready interrupt clear) — установка этого бита в единицу позволяет очистить флаг HSIRDYF.

LSERDYC(LSE ready interrupt clear) — установка этого бита в единицу позволяет очистить флаг LSERDYF.

LSIRDYC(LSI ready interrupt clear) — установка этого бита в единицу позволяет очистить флаг LSIRDYF

PLLRDYIE(PLL ready interrupt enable) — единица в этом бите разрешает прерывания при сцеплении PLL.

HSERDYIE(HSE ready interrupt enable) — единица в этом бите разрешает прерывания при сцеплении HSE.

HSIRDYIE(HSI ready interrupt enable) — единица в этом бите разрешает прерывания при сцеплении HSI.

LSERDYIE(LSE ready interrupt enable) — единица в этом бите разрешает прерывания при сцеплении LSE.

LSIRDYIE(LSI ready interrupt enable) — единица в этом бите разрешает прерывания при сцеплении LSI.

CSSF(Clock security system interrupt flag) — этот флаг устанавливается аппаратно при отказе HSE, очищается с помощью CSSC.

PLLRDYF(PLL ready interrupt flag) — этот флаг устанавливается аппаратно если произошло сцеплении с PLL и бит PLLRDYDIE установлен..

HSERDYF(HSE ready interrupt flag) — этот флаг устанавливается аппаратно если HSE стабилизировался и бит HSERDYDIE установлен.

HSIRDYF(HSI ready interrupt flag) — этот флаг устанавливается аппаратно если HSI стабилизировался и бит HSIRDYDIE установлен..

LSERDYF(LSE ready interrupt flag) — этот флаг устанавливается аппаратно если LSE стабилизировался и бит LSERDYDIE установлен..

LSIRDYF(LSI ready interrupt flag) — этот флаг устанавливается аппаратно если LSI стабилизировался и бит LSIRDYDIE установлен.

Регистр сброса RCC_APB2RSTR

При записи единицы в биты этого регистра происходит сброс соответствующей периферии, которая тактируется от шины APB2. Под сбросом понимается установка в регистры блока, например USART, значения по умолчанию.

Регистр сброса RCC_APB1RSTR

При записи единицы в биты этого регистра происходит сброс соответствующей периферии, которая тактируется от шины APB1. Под сбросом понимается установка в регистры блока, например USART, значения по умолчанию.

Регистр управления тактированием на шине AHB RCC_AHBENR

При записи единицы в биты этого регистра включается тактирование соответствующей периферии подключенной к шине AHB, при записи нуля отключается.

Регистр управления тактированием на шине APB2 RCC_APB2ENR

При записи единицы в биты этого регистра включается тактирование соответствующей периферии подключенной к шине APB2, при записи нуля отключается.

Регистр управления тактированием на шине APB1 RCC_APB1ENR

При записи единицы в биты этого регистра включается тактирование соответствующей периферии подключенной к шине APB1, при записи нуля отключается.

Регистр управления доменом BKP RCC_BDCR:

BDRST(Backup domain software reset) — установка единицы в этот бит сбрасывает значение битов регистра RCC_BDCR.

RTCEN(RTC clock enable) — установка единицы в этот бит включает тактирование RTC.

RTCSEL[1:0](RTC clock source selection) — значение этих битов определяет источник тактирования RTC.

LSEBYP(External low-speed oscillator bypass) — ставится и очищается программно, чтобы обойти LSE генератор в режиме отладки.

LSERDY(External low-speed oscillator ready) — единица в этом бите говорит о том, что LSE с частотой 32KHz стабилизировался.

LSEON(External low-speed oscillator enable) — установка единицы в этот бит разрешает работу LSE с частотой 32KHz.

Регистр управления/статуса RCC_CSR:

LPWRRSTF(Low-power reset flag) — этот флаг устанавливается аппаратно, когда происходит от контроллера пониженного потребления.

WWDGRSTF(Window watchdog reset flag) — этот флаг устанавливается аппаратно, когда происходит сброс от оконного WatchDog.

IWDGRSTF(Independent watchdog reset flag) — этот флаг устанавливается аппаратно, когда происходит сброс от независимого WatchDog.

SFTRSTF(Software reset flag) — этот флаг устанавливается аппаратно, когда происходит программный сброс.

PORRSTF(POR/PDR reset flag) — этот флаг устанавливается аппаратно при при включение/выключение питания.

PINRSTF(PIN reset flag) — этот флаг устанавливается аппаратно, когда происходит сброс от вывода NRST.

RMVF(Remove reset flag) — установка единицы в этот бит позволяет сбросить все, описанные выше флаги, в этот регистре.

LSIRDY(Internal low-speed oscillator ready) — единица в этом бите говорит о том, что LSI стабилизировался.

LSION(Internal low-speed oscillator enable) — установка единицы в этот бит разрешает работу внутреннего RC генератора 40 kHz.

На самом деле, до сих пор выбираю частоту тактирования системной шины в файле system_stm32f10x.c, просто раскоментировав нужную строку, но теперь это делаю осознано.

Похожие статьи