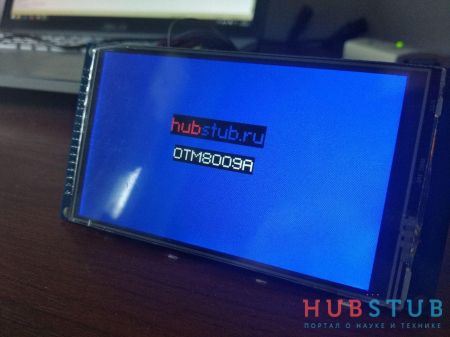

Инициализация TFT дисплея OTM8009A.

Ровно пять лет прошло с того момента, как на сайте появилась первая статья, описывавшая инициализацию дисплея. В своих проектах я использовал его не один год и за это время, в продаже появились дисплеи, обладающие лучшими характеристиками. Например, IPS дисплей размером 3.97 дюйма, с разрешением 800x480 пикселей.

Подключается он по интерфейсу i8080, который не однократно описывал в других статьях и думаю, очередной раз описывать этот интерфейс не имеет смысла. А вот описать инициализацию дисплея смысл имеет.

Дисплей покупал тут.

Подключается он по интерфейсу i8080, который не однократно описывал в других статьях и думаю, очередной раз описывать этот интерфейс не имеет смысла. А вот описать инициализацию дисплея смысл имеет.

#define LCD_H 480

#define LCD_W 800

static void TFT_Send_Cmd(uint16_t cmd)

{

TFT_RS_LOW

//TFT_RD_HIGH

GPIOD->ODR = cmd;

TFT_WR_LOW

TFT_WR_HIGH

TFT_RS_HIGH

}

static void TFT_Write_Data(uint16_t data)

{

//TFT_RS_HIGH

//TFT_RD_HIGH

GPIOD->ODR = data;

TFT_WR_LOW

TFT_WR_HIGH

}

////////////////////////////////////////

void Init_OTM8009A(void)

{

//D0 - PD0

//..

//..

//..

//D14 - PD15

//RS - PB5

//CS - PB6

//RD - PB7

//WR - PB8

//RST - PB3

RCC->AHB1ENR |= RCC_AHB1ENR_GPIOBEN | RCC_AHB1ENR_GPIODEN;

//настраиваем все выходы как PP

GPIOB->MODER |= (GPIO_MODER_MODER3_0 | GPIO_MODER_MODER5_0 | GPIO_MODER_MODER6_0 |

GPIO_MODER_MODER7_0 | GPIO_MODER_MODER8_0);

GPIOD->MODER = (GPIO_MODER_MODER0_0 | GPIO_MODER_MODER1_0 | GPIO_MODER_MODER2_0 | GPIO_MODER_MODER3_0 |

GPIO_MODER_MODER4_0 |GPIO_MODER_MODER5_0 | GPIO_MODER_MODER6_0 | GPIO_MODER_MODER7_0 |

GPIO_MODER_MODER8_0 | GPIO_MODER_MODER9_0 | GPIO_MODER_MODER10_0 | GPIO_MODER_MODER11_0 |

GPIO_MODER_MODER12_0 | GPIO_MODER_MODER13_0 | GPIO_MODER_MODER14_0 | GPIO_MODER_MODER15_0);

GPIOB->OSPEEDR = (GPIO_OSPEEDER_OSPEEDR3 | GPIO_OSPEEDER_OSPEEDR5 | GPIO_OSPEEDER_OSPEEDR6 | GPIO_OSPEEDER_OSPEEDR7 |

GPIO_OSPEEDER_OSPEEDR8);

GPIOD->OSPEEDR = (GPIO_OSPEEDER_OSPEEDR0 | GPIO_OSPEEDER_OSPEEDR1 | GPIO_OSPEEDER_OSPEEDR2 | GPIO_OSPEEDER_OSPEEDR3 |

GPIO_OSPEEDER_OSPEEDR4 | GPIO_OSPEEDER_OSPEEDR5 | GPIO_OSPEEDER_OSPEEDR6 | GPIO_OSPEEDER_OSPEEDR7 |

GPIO_OSPEEDER_OSPEEDR8 | GPIO_OSPEEDER_OSPEEDR9 | GPIO_OSPEEDER_OSPEEDR10 | GPIO_OSPEEDER_OSPEEDR11 |

GPIO_OSPEEDER_OSPEEDR12 | GPIO_OSPEEDER_OSPEEDR13 | GPIO_OSPEEDER_OSPEEDR14 | GPIO_OSPEEDER_OSPEEDR15);

//управляющие сигналы устанавливаем в высокой уровень и учитываем это, чтобы лишний раз их не дергать

TFT_RS_HIGH

TFT_RD_HIGH

TFT_WR_HIGH

TFT_CS_LOW

// Reset дисплея

TFT_RST_LOW

delay_ms(2);

TFT_RST_HIGH

delay_ms(100);

//3.97inch OTM8009 Init

TFT_Send_Cmd(0xff00);

TFT_Write_Data(0x80);

TFT_Send_Cmd(0xff01);

TFT_Write_Data(0x09);

TFT_Send_Cmd(0xff02);

TFT_Write_Data(0x01);

TFT_Send_Cmd(0xff80);

TFT_Write_Data(0x80);

TFT_Send_Cmd(0xff81);

TFT_Write_Data(0x09);

TFT_Send_Cmd(0xff03);

TFT_Write_Data(0x01);

TFT_Send_Cmd(0xf5b6);

TFT_Write_Data(0x06);

TFT_Send_Cmd(0xc480);

TFT_Write_Data(0x30);

TFT_Send_Cmd(0xc48a);

TFT_Write_Data(0x40);

//===================================================//

TFT_Send_Cmd(0xc0a3);

TFT_Write_Data(0x1B);

//TFT_Send_Cmd(0xc0ba);

//TFT_Write_Data(0x50);

TFT_Send_Cmd(0xc0ba);

TFT_Write_Data(0x50);

TFT_Send_Cmd(0xc181);

TFT_Write_Data(0x66);

TFT_Send_Cmd(0xc1a1);

TFT_Write_Data(0x0E);

TFT_Send_Cmd(0xc481);

TFT_Write_Data(0x83);

TFT_Send_Cmd(0xc582);

TFT_Write_Data(0x83);

TFT_Send_Cmd(0xc590);

TFT_Write_Data(0x96);

TFT_Send_Cmd(0xc591);

TFT_Write_Data(0x2B);

TFT_Send_Cmd(0xc592);

TFT_Write_Data(0x01);

TFT_Send_Cmd(0xc594);

TFT_Write_Data(0x33);

TFT_Send_Cmd(0xc595);

TFT_Write_Data(0x34);

TFT_Send_Cmd(0xc5b1);

TFT_Write_Data(0xa9);

TFT_Send_Cmd(0xce80);

TFT_Write_Data(0x86);

TFT_Send_Cmd(0xce81);

TFT_Write_Data(0x01);

TFT_Send_Cmd(0xce82);

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xce83);

TFT_Write_Data(0x85);

TFT_Send_Cmd(0xce84);

TFT_Write_Data(0x01);

TFT_Send_Cmd(0xce85);

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xce86);

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xce87);

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xce88);

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xce89);

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xce8A);

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xce8B);

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcea0);// cea1[7:0] : clka1_width[3:0], clka1_shift[11:8]

TFT_Write_Data(0x18);

TFT_Send_Cmd(0xcea1);// cea2[7:0] : clka1_shift[7:0]

TFT_Write_Data(0x04);

TFT_Send_Cmd(0xcea2);// cea3[7:0] : clka1_sw_tg, odd_high, flat_head, flat_tail, switch[11:8]

TFT_Write_Data(0x03);

TFT_Send_Cmd(0xcea3);// cea4[7:0] : clka1_switch[7:0]

TFT_Write_Data(0x21);

TFT_Send_Cmd(0xcea4);// cea5[7:0] : clka1_extend[7:0]

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcea5);// cea6[7:0] : clka1_tchop[7:0]

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcea6);// cea7[7:0] : clka1_tglue[7:0]

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcea7);// cea8[7:0] : clka2_width[3:0], clka2_shift[11:8]

TFT_Write_Data(0x18);

TFT_Send_Cmd(0xcea8);// cea9[7:0] : clka2_shift[7:0]

TFT_Write_Data(0x03);

TFT_Send_Cmd(0xcea9);// ceaa[7:0] : clka2_sw_tg, odd_high, flat_head, flat_tail, switch[11:8]

TFT_Write_Data(0x03);

TFT_Send_Cmd(0xceaa);// ceab[7:0] : clka2_switch[7:0]

TFT_Write_Data(0x22);

TFT_Send_Cmd(0xceab);// ceac[7:0] : clka2_extend

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xceac);// cead[7:0] : clka2_tchop

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcead);// ceae[7:0] : clka2_tglue

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xceb0);// ceb1[7:0] : clka3_width[3:0], clka3_shift[11:8]

TFT_Write_Data(0x18);

TFT_Send_Cmd(0xceb1);// ceb2[7:0] : clka3_shift[7:0]

TFT_Write_Data(0x02);

TFT_Send_Cmd(0xceb2);// ceb3[7:0] : clka3_sw_tg, odd_high, flat_head, flat_tail, switch[11:8]

TFT_Write_Data(0x03);

TFT_Send_Cmd(0xceb3);// ceb4[7:0] : clka3_switch[7:0]

TFT_Write_Data(0x23);

TFT_Send_Cmd(0xceb4);// ceb5[7:0] : clka3_extend[7:0]

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xceb5);// ceb6[7:0] : clka3_tchop[7:0]

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xceb6);// ceb7[7:0] : clka3_tglue[7:0]

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xceb7);// ceb8[7:0] : clka4_width[3:0], clka2_shift[11:8]

TFT_Write_Data(0x18);

TFT_Send_Cmd(0xceb8);// ceb9[7:0] : clka4_shift[7:0]

TFT_Write_Data(0x01);

TFT_Send_Cmd(0xceb9);// ceba[7:0] : clka4_sw_tg, odd_high, flat_head, flat_tail, switch[11:8]

TFT_Write_Data(0x03);

TFT_Send_Cmd(0xceba);// cebb[7:0] : clka4_switch[7:0]

TFT_Write_Data(0x24);

TFT_Send_Cmd(0xcebb);// cebc[7:0] : clka4_extend

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcebc);// cebd[7:0] : clka4_tchop

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcebd);// cebe[7:0] : clka4_tglue

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcfc0);// cfc1[7:0] : eclk_normal_width[7:0]

TFT_Write_Data(0x01);

TFT_Send_Cmd(0xcfc1);// cfc2[7:0] : eclk_partial_width[7:0]

TFT_Write_Data(0x01);

TFT_Send_Cmd(0xcfc2);// cfc3[7:0] : all_normal_tchop[7:0]

TFT_Write_Data(0x20);

TFT_Send_Cmd(0xcfc3);// cfc4[7:0] : all_partial_tchop[7:0]

TFT_Write_Data(0x20);

TFT_Send_Cmd(0xcfc4);// cfc5[7:0] : eclk1_follow[3:0], eclk2_follow[3:0]

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcfc5);// cfc6[7:0] : eclk3_follow[3:0], eclk4_follow[3:0]

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcfc6);// cfc7[7:0] : 00, vstmask, vendmask, 00, dir1, dir2 (0=VGL, 1=VGH)

TFT_Write_Data(0x01);

TFT_Send_Cmd(0xcfc7);// cfc8[7:0] : reg_goa_gnd_opt, reg_goa_dpgm_tail_set, reg_goa_f_gating_en, reg_goa_f_odd_gating, toggle_mod1, 2, 3, 4

TFT_Write_Data(0x00); // GND OPT1 (00-->80 2011/10/28)

TFT_Send_Cmd(0xcfc8);// cfc9[7:0] : duty_block[3:0], DGPM[3:0]

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcfc9);// cfca[7:0] : reg_goa_gnd_period[7:0]

TFT_Write_Data(0x00); // Gate PCH (CLK base) (00-->0a 2011/10/28)

TFT_Send_Cmd(0xcfd0);// cfd1[7:0] : 0000000, reg_goa_frame_odd_high

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbc0);//cbc1[7:0] : enmode H-byte of sig1 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbc1);//cbc2[7:0] : enmode H-byte of sig2 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x04);

TFT_Send_Cmd(0xcbc2);//cbc3[7:0] : enmode H-byte of sig3 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x04);

TFT_Send_Cmd(0xcbc3);//cbc4[7:0] : enmode H-byte of sig4 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x04);

TFT_Send_Cmd(0xcbc4);//cbc5[7:0] : enmode H-byte of sig5 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x04);

TFT_Send_Cmd(0xcbc5);//cbc6[7:0] : enmode H-byte of sig6 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x04);

TFT_Send_Cmd(0xcbc6);//cbc7[7:0] : enmode H-byte of sig7 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbc7);//cbc8[7:0] : enmode H-byte of sig8 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbc8);//cbc9[7:0] : enmode H-byte of sig9 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbc9);//cbca[7:0] : enmode H-byte of sig10 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbca);//cbcb[7:0] : enmode H-byte of sig11 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbcb);//cbcc[7:0] : enmode H-byte of sig12 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbcc);//cbcd[7:0] : enmode H-byte of sig13 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbcd);//cbce[7:0] : enmode H-byte of sig14 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbce);//cbcf[7:0] : enmode H-byte of sig15 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbd0);//cbd1[7:0] : enmode H-byte of sig16 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbd1);//cbd2[7:0] : enmode H-byte of sig17 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbd2);//cbd3[7:0] : enmode H-byte of sig18 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbd3);//cbd4[7:0] : enmode H-byte of sig19 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbd4);//cbd5[7:0] : enmode H-byte of sig20 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbd5);//cbd6[7:0] : enmode H-byte of sig21 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbd6);//cbd7[7:0] : enmode H-byte of sig22 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x04);

TFT_Send_Cmd(0xcbd7);//cbd8[7:0] : enmode H-byte of sig23 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x04);

TFT_Send_Cmd(0xcbd8);//cbd9[7:0] : enmode H-byte of sig24 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x04);

TFT_Send_Cmd(0xcbd9);//cbda[7:0] : enmode H-byte of sig25 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x04);

TFT_Send_Cmd(0xcbda);//cbdb[7:0] : enmode H-byte of sig26 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x04);

TFT_Send_Cmd(0xcbdb);//cbdc[7:0] : enmode H-byte of sig27 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbdc);//cbdd[7:0] : enmode H-byte of sig28 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbdd);//cbde[7:0] : enmode H-byte of sig29 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbde);//cbdf[7:0] : enmode H-byte of sig30 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbe0);//cbe1[7:0] : enmode H-byte of sig31 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbe1);//cbe2[7:0] : enmode H-byte of sig32 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbe2);//cbe3[7:0] : enmode H-byte of sig33 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbe3);//cbe4[7:0] : enmode H-byte of sig34 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbe4);//cbe5[7:0] : enmode H-byte of sig35 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbe5);//cbe6[7:0] : enmode H-byte of sig36 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbe6);//cbe7[7:0] : enmode H-byte of sig37 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbe7);//cbe8[7:0] : enmode H-byte of sig38 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbe8);//cbe9[7:0] : enmode H-byte of sig39 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcbe9);//cbea[7:0] : enmode H-byte of sig40 (pwrof_0, pwrof_1, norm, pwron_4 )

TFT_Write_Data(0x00);

// cc8x

TFT_Send_Cmd(0xcc80);//cc81[7:0] : reg setting for signal01 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcc81);//cc82[7:0] : reg setting for signal02 selection with u2d mode

TFT_Write_Data(0x26);

TFT_Send_Cmd(0xcc82);//cc83[7:0] : reg setting for signal03 selection with u2d mode

TFT_Write_Data(0x09);

TFT_Send_Cmd(0xcc83);//cc84[7:0] : reg setting for signal04 selection with u2d mode

TFT_Write_Data(0x0B);

TFT_Send_Cmd(0xcc84);//cc85[7:0] : reg setting for signal05 selection with u2d mode

TFT_Write_Data(0x01);

TFT_Send_Cmd(0xcc85);//cc86[7:0] : reg setting for signal06 selection with u2d mode

TFT_Write_Data(0x25);

TFT_Send_Cmd(0xcc86);//cc87[7:0] : reg setting for signal07 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcc87);//cc88[7:0] : reg setting for signal08 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcc88);//cc89[7:0] : reg setting for signal09 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcc89);//cc8a[7:0] : reg setting for signal10 selection with u2d mode

TFT_Write_Data(0x00);

// cc9x

TFT_Send_Cmd(0xcc90);//cc91[7:0] : reg setting for signal11 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcc91);//cc92[7:0] : reg setting for signal12 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcc92);//cc93[7:0] : reg setting for signal13 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcc93);//cc94[7:0] : reg setting for signal14 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcc94);//cc95[7:0] : reg setting for signal15 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcc95);//cc96[7:0] : reg setting for signal16 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcc96);//cc97[7:0] : reg setting for signal17 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcc97);//cc98[7:0] : reg setting for signal18 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcc98);//cc99[7:0] : reg setting for signal19 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcc99);//cc9a[7:0] : reg setting for signal20 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcc9a);//cc9b[7:0] : reg setting for signal21 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcc9b);//cc9c[7:0] : reg setting for signal22 selection with u2d mode

TFT_Write_Data(0x26);

TFT_Send_Cmd(0xcc9c);//cc9d[7:0] : reg setting for signal23 selection with u2d mode

TFT_Write_Data(0x0A);

TFT_Send_Cmd(0xcc9d);//cc9e[7:0] : reg setting for signal24 selection with u2d mode

TFT_Write_Data(0x0C);

TFT_Send_Cmd(0xcc9e);//cc9f[7:0] : reg setting for signal25 selection with u2d mode

TFT_Write_Data(0x02);

// ccax

TFT_Send_Cmd(0xcca0);//cca1[7:0] : reg setting for signal26 selection with u2d mode

TFT_Write_Data(0x25);

TFT_Send_Cmd(0xcca1);//cca2[7:0] : reg setting for signal27 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcca2);//cca3[7:0] : reg setting for signal28 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcca3);//cca4[7:0] : reg setting for signal29 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcca4);//cca5[7:0] : reg setting for signal20 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcca5);//cca6[7:0] : reg setting for signal31 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcca6);//cca7[7:0] : reg setting for signal32 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcca7);//cca8[7:0] : reg setting for signal33 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcca8);//cca9[7:0] : reg setting for signal34 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0xcca9);//ccaa[7:0] : reg setting for signal35 selection with u2d mode

TFT_Write_Data(0x00);

TFT_Send_Cmd(0x3A00);//ccaa[7:0] : reg setting for signal35 selection with u2d mode

TFT_Write_Data(0x55);//0x55

TFT_Send_Cmd(0x1100);

delay_ms(100);

TFT_Send_Cmd(0x2900);

delay_ms(50);

TFT_Send_Cmd(0x2C00);

TFT_Send_Cmd(0x3600);//выбираем ориентацию дисплея и порядок цветов BGR

TFT_Write_Data((1<<3)|(1<<5)|(1<<6));

delay_ms(100);

TFT_Clear(GREEN);

}

////////////////////////

void TFT_Set_Column(uint16_t start_column,uint16_t end_colunm)

{

TFT_Send_Cmd(0x2A00);

TFT_Write_Data(start_column>>8);

TFT_Send_Cmd(0x2A01);

TFT_Write_Data(start_column&0x00FF);

TFT_Send_Cmd(0x2A02);

TFT_Write_Data(end_colunm>>8);

TFT_Send_Cmd(0x2A03);

TFT_Write_Data(end_colunm&0x00FF);

}

/////////////////////////

void TFT_Set_Page(uint16_t start_page,uint16_t end_page)

{

TFT_Send_Cmd(0x2B00);

TFT_Write_Data(start_page>>8);

TFT_Send_Cmd(0x2B01);

TFT_Write_Data(start_page&0x00FF);

TFT_Send_Cmd(0x2B02);

TFT_Write_Data(end_page>>8);

TFT_Send_Cmd(0x2B03);

TFT_Write_Data(end_page&0x00FF);

}

////////////////////////

void TFT_Clear(uint16_t color)

{

uint32_t index = 0;

TFT_Set_Page(0,LCD_H-1);

TFT_Set_Column(0,LCD_W-1);

TFT_Send_Cmd(0x2C00);

for(index=0;index<(LCD_H*LCD_W);index++)

{

TFT_Write_Data(color);

}

}

//////////////////

Дисплей покупал тут.

Похожие статьи