Первая программа для ПЛИС на Verilog.

В одной из прошлых статей, описывал как прошить ПЛИС уже имеющейся прошивкой, в этой попробуем написать прошивку сами. Начнем с простого — помигаем светодиодом. Для написания программы мы будем использовать язык похожий на С — Verilog.

Для начала создадим проект.

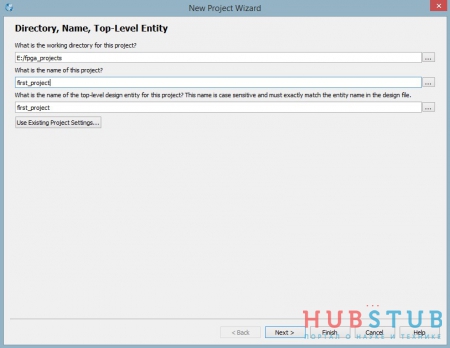

Указываем папку, в которой будет храниться проект, название проекта и название модуля верхнего уровня.

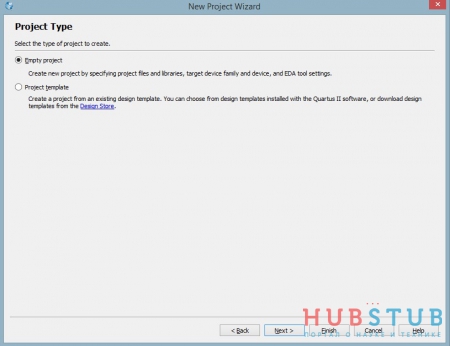

Указываем, что проект будет пустой.

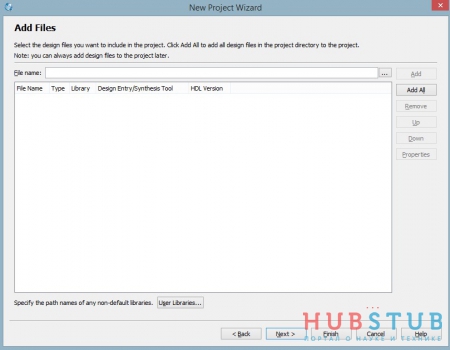

На этом шаге инклудятся файлы, мы его пропускаем.

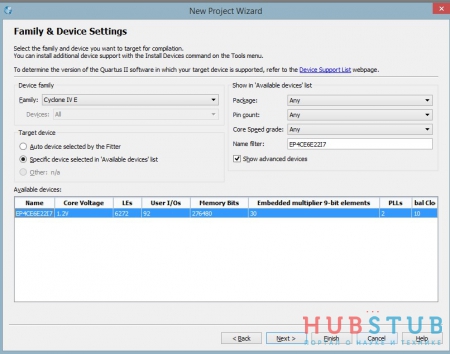

Выбираем камешек, который будем программировать.

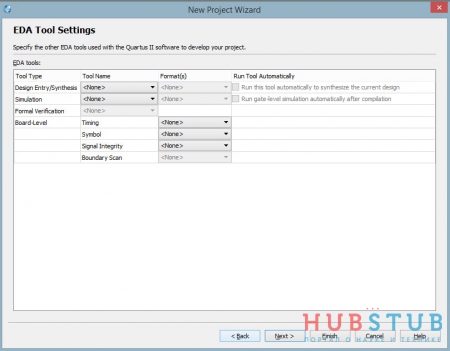

На этом шаге предлагается выбрать средства отладки проекта, мы его пропускаем.

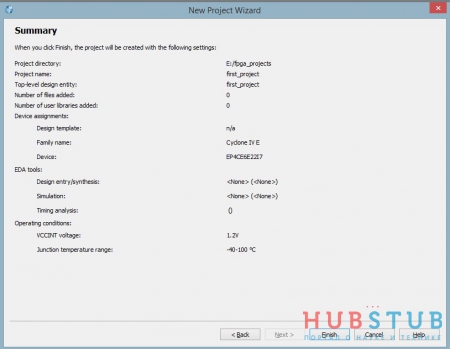

Чек лист для проверки настроек проекта. Если необходимо, любую из настроек можно изменить, вернувшись на несколько шагов назад, используя кнопку Back.

Думаю у многих возник вопрос, что такое модуль верхнего уровня?

Входы и выходы модуля верхнего уровня соединяются непосредственно с выводами микросхемы, также модуль верхнего уровня включает в себя все остальные модули.

Так как проект у нас простой, модуль у нас будет всего один и он же будет модулем верхнего уровня.

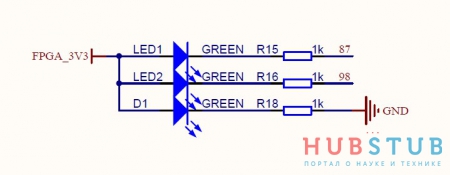

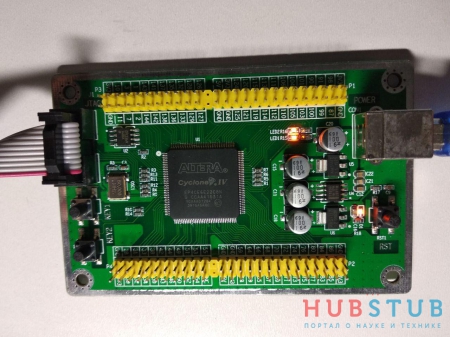

После того как проект создан, откроем схему отладочной платы и посмотрим к какому выводу подключен светодиод и на какой вывод подается тактирование с генератора.

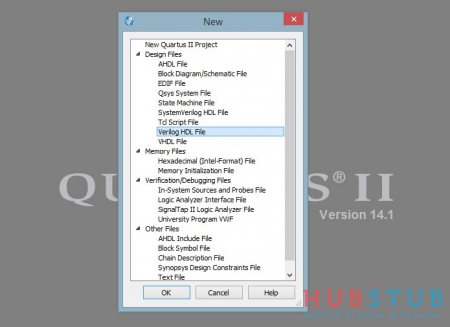

Теперь можно переходить непосредственно к написанию программы. Создаем новый Verilog HDL File, во вкладке File->New.

И пишем следующий код, который изменяет состояние светодиодов два раза в секунду.

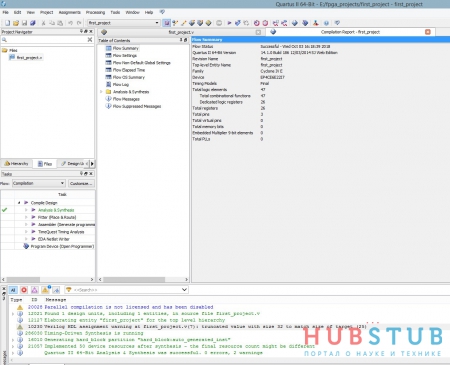

Далее синтезируем проект.

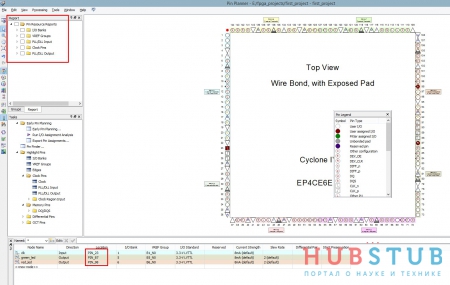

Теперь нужно назначить сигналам реальные выводы микросхемы во вкладке Pin Planner.

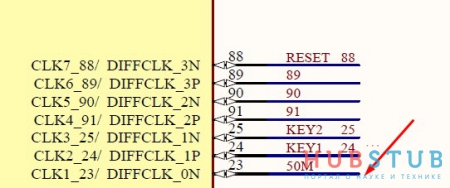

В столбце location указал какие выводы каким сигналам будут соответствовать. Хотелось бы отметить, что нельзя назначить сигналу любой вывод микросхемы потому, что сигналы разделены на 5 групп и каждая из них имеет свое назначение, на скриншоте они выделены красным квадратом. Первая группа — привычные выводы входа/выхода, на вторую группу заводятся опорные напряжения для каждого банка отдельно, третья и пятая - это вход и выход PLL, а на выводы четвертой группы заводится тактовый сигнал.

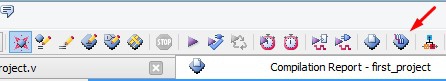

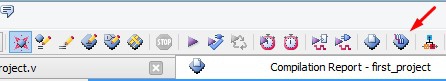

Теперь необходимо запустить компиляцию.

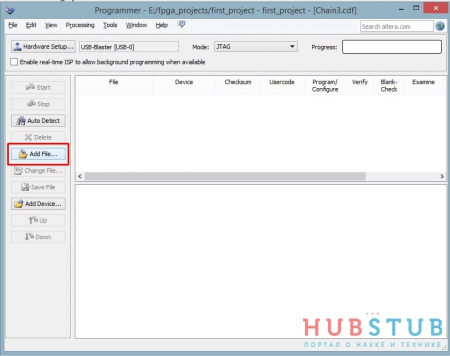

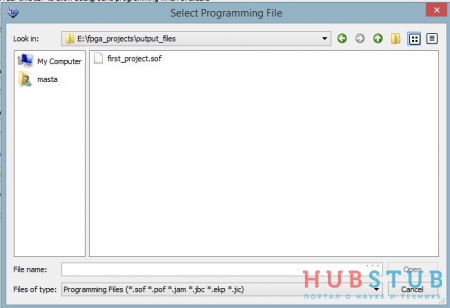

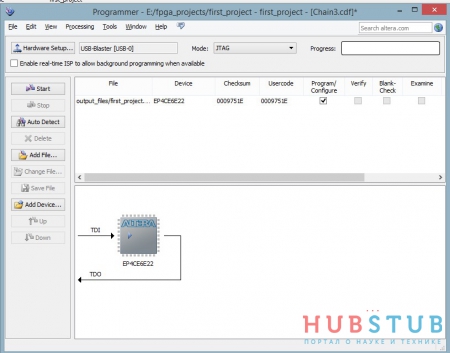

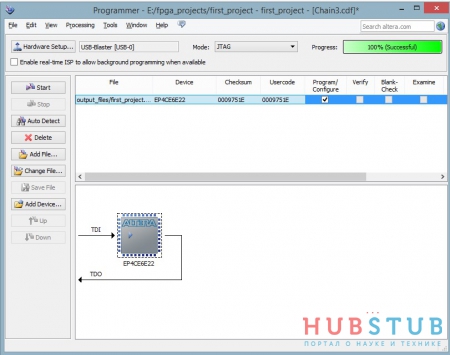

В результате компиляции генерируется файл .sof, который можно зашить в ПЛИС.

Для начала создадим проект.

Указываем папку, в которой будет храниться проект, название проекта и название модуля верхнего уровня.

Указываем, что проект будет пустой.

На этом шаге инклудятся файлы, мы его пропускаем.

Выбираем камешек, который будем программировать.

На этом шаге предлагается выбрать средства отладки проекта, мы его пропускаем.

Чек лист для проверки настроек проекта. Если необходимо, любую из настроек можно изменить, вернувшись на несколько шагов назад, используя кнопку Back.

Думаю у многих возник вопрос, что такое модуль верхнего уровня?

Входы и выходы модуля верхнего уровня соединяются непосредственно с выводами микросхемы, также модуль верхнего уровня включает в себя все остальные модули.

Так как проект у нас простой, модуль у нас будет всего один и он же будет модулем верхнего уровня.

После того как проект создан, откроем схему отладочной платы и посмотрим к какому выводу подключен светодиод и на какой вывод подается тактирование с генератора.

Теперь можно переходить непосредственно к написанию программы. Создаем новый Verilog HDL File, во вкладке File->New.

И пишем следующий код, который изменяет состояние светодиодов два раза в секунду.

module first_project(input clk, output reg red_led, output reg green_led);

reg[24:0] counter;

always@(posedge clk)

begin

counter<=counter+1;

if(counter == 25'd25000000)

begin

green_led <= green_led^1'b1;

red_led <= red_led^1'b1;

counter <= 0;

end

end

endmodule

Далее синтезируем проект.

Теперь нужно назначить сигналам реальные выводы микросхемы во вкладке Pin Planner.

В столбце location указал какие выводы каким сигналам будут соответствовать. Хотелось бы отметить, что нельзя назначить сигналу любой вывод микросхемы потому, что сигналы разделены на 5 групп и каждая из них имеет свое назначение, на скриншоте они выделены красным квадратом. Первая группа — привычные выводы входа/выхода, на вторую группу заводятся опорные напряжения для каждого банка отдельно, третья и пятая - это вход и выход PLL, а на выводы четвертой группы заводится тактовый сигнал.

Теперь необходимо запустить компиляцию.

В результате компиляции генерируется файл .sof, который можно зашить в ПЛИС.

Похожие статьи